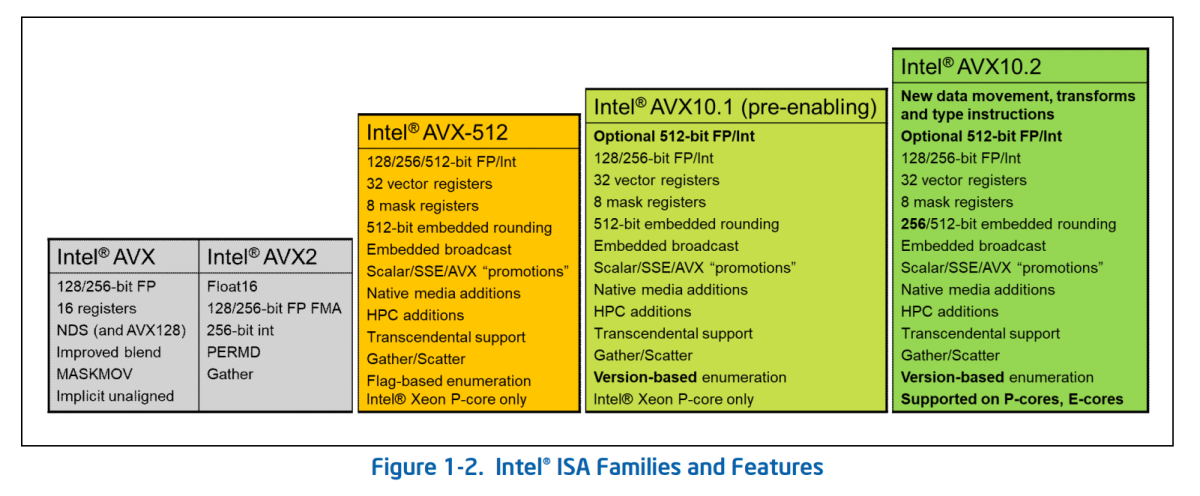

Intel publicó hoy su nuevo APX (Advanced Performance Extensions) y también lanzó el nuevo AVX10 [PDF] que brindará soporte unificado para las funciones AVX-512 para P-Core y E-Core por primera vez. Esta evolución del conjunto de instrucciones AVX ayudará a Intel a superar los graves problemas encontrados con su nueva arquitectura híbrida x86 que se encuentran en los procesadores Alder y Raptor Lake.

Sin embargo, este nuevo ISA no será compatible con los procesadores de la generación actual de Intel; está previsto que llegue a los futuros chips. Intel dice que AVX10 será su vector ISA de elección en el futuro tanto para procesadores de consumo como de servidor.

En su nivel más básico, AVX10 permitirá que los chips Intel que tienen núcleos E y núcleos P sigan siendo compatibles con AVX-512, aunque las instrucciones de 512 bits solo se pueden ejecutar en núcleos P. Mientras tanto, las instrucciones convergentes de 256 bits se pueden ejecutar en p-cores o e-cores, lo que permite que el chip completo siga siendo compatible con las funciones AVX-512.

(Crédito de la imagen: Intel)

El AV10 (Advanced Instruction Extensions 10) ISA es un superconjunto del AVX-512 y viene con todas las características del AVX-512 ISA para procesadores con tamaños de registro vectorial de 256 bits y 512 bits.

El ISA convergente AVX10 incluirá «instrucciones vectoriales AVX-512 con un indicador de función AVX512VL, una longitud máxima de registro vectorial de 256 bits, así como ocho registros de máscara de 32 bits y nuevas versiones de instrucciones de 256 bits con soporte para redondeo integrado», y esta versión se ejecutará en colores p y colores electrónicos.

Sin embargo, los núcleos electrónicos se limitarán a la longitud de vector convergente máxima de 256 bits de AVX10, mientras que los núcleos P pueden usar vectores de 512 bits. Esto se parece al soporte de Arm para anchos de vector variables con SVE.

Intel dice que las aplicaciones existentes proporcionarán el mismo nivel de rendimiento con el AVX10 que con el AVX-512, al menos con las mismas longitudes de vector. Intel también afirma:

- Las aplicaciones compiladas para Intel AVX2 recompiladas para Intel AVX10 deberían ver mejoras en el rendimiento sin necesidad de ajustes de software adicionales.

- Las aplicaciones Intel AVX2 sensibles a la presión del registro vectorial obtendrán el máximo rendimiento gracias a los 16 registros vectoriales adicionales y las nuevas instrucciones.

- Es probable que las aplicaciones vectorizables con muchos subprocesos logren un mayor rendimiento agregado cuando se ejecutan en procesadores Intel Xeon basados en E-core o productos Intel de arquitectura híbrida de rendimiento.

Intel admitirá AVX10 versión 1 (AVX10.1) a partir de sus chips Xeon «Granite Rapids» de sexta generación, pero esa generación solo admitirá instrucciones vectoriales de 512 bits, no las nuevas instrucciones vectoriales convergentes de 256 bits. En cambio, esta primera generación servirá como un chip de transición del AVX-512 al AVX10.

AVX10.2 admitirá longitudes de matriz de 256 bits y otras características nuevas, como nuevos tipos y conversiones de datos de IA, optimizaciones de movimiento de datos y compatibilidad con estándares. Todos los futuros procesadores Xeon seguirán siendo totalmente compatibles con todas las instrucciones AVX-512 para garantizar que las aplicaciones heredadas funcionen sin problemas.

(Crédito de la imagen: Intel)

Para abordar los comentarios de los desarrolladores, Intel también planea simplificar significativamente sus métodos de enumeración AVX10 en comparación con AVX-512, e Intel también planea garantizar que cada cambio a una nueva revisión tenga suficientes instrucciones y características nuevas para merecer un cambio, reduciendo así la versión y la enumeración.

Intel congelará el AVX-512 ISA cuando se lance AVX10, y todo uso futuro de las instrucciones AVX-512 será a través del AVX10 ISA.